Home

Project Audio Signal Processing - System on Chip

Abstract

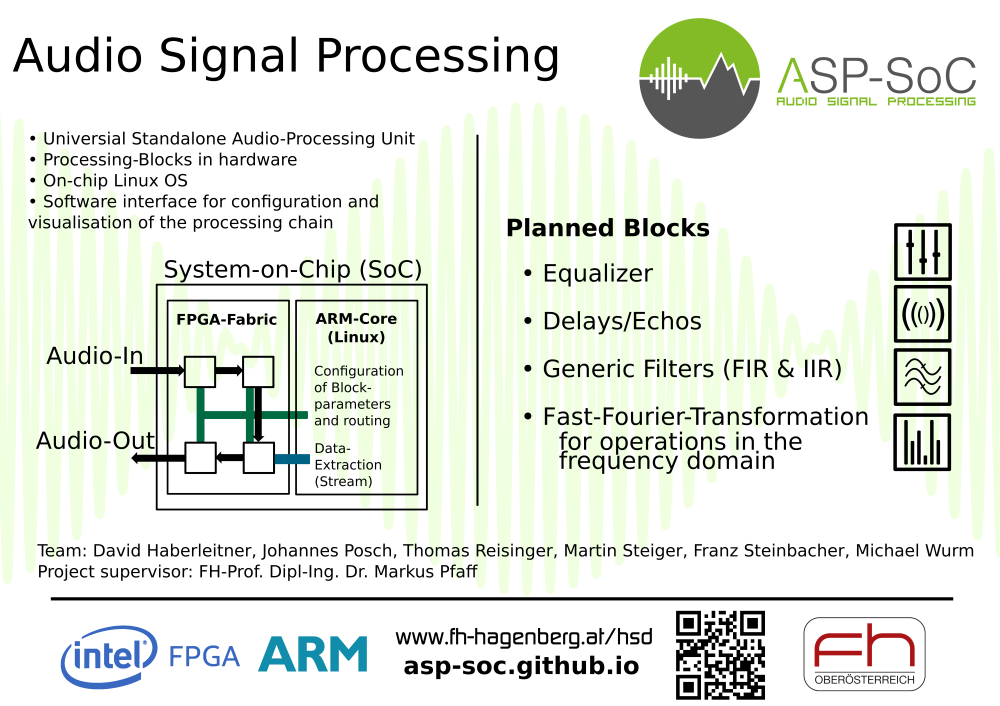

The aim of this project is to create a universal standalone customizable audio signal processing chain on a FPGA SoC.

The audio processing is realized in hardware and the configuration/visualisation interface is based on a Linux OS on the ARM Core of the system. The software is based on a webpage which is hosted on the OS, so you easily can access it with any device with a webbrowser, such as your PC, Laptop or Smartphone.

The platform is fully configurable, so you simply can change the routing or add new components/blocks to the processing chain.

Planned blocks are:

- Equalizer

- Audio Effects

- Generic Filters

- Spectral Analysis

- Signal Generator

The Hardware Design is written in VHDL, the simulation is done with ModelSim and the Synthesis with Quartus Prime.

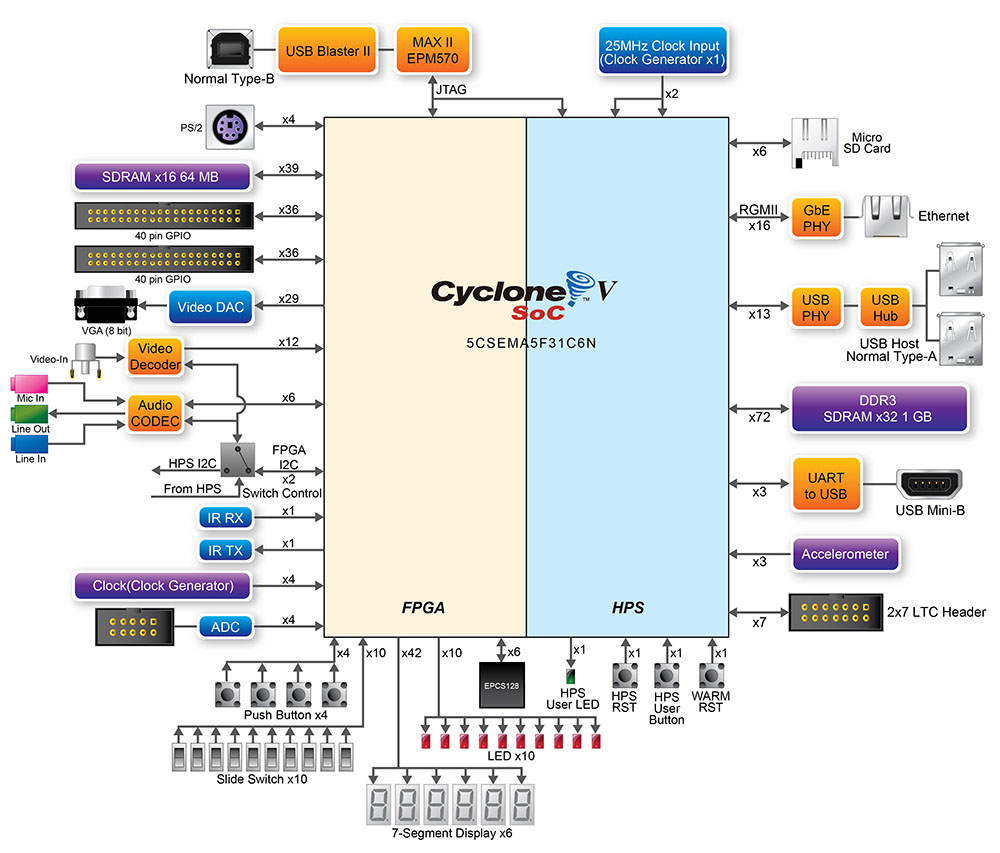

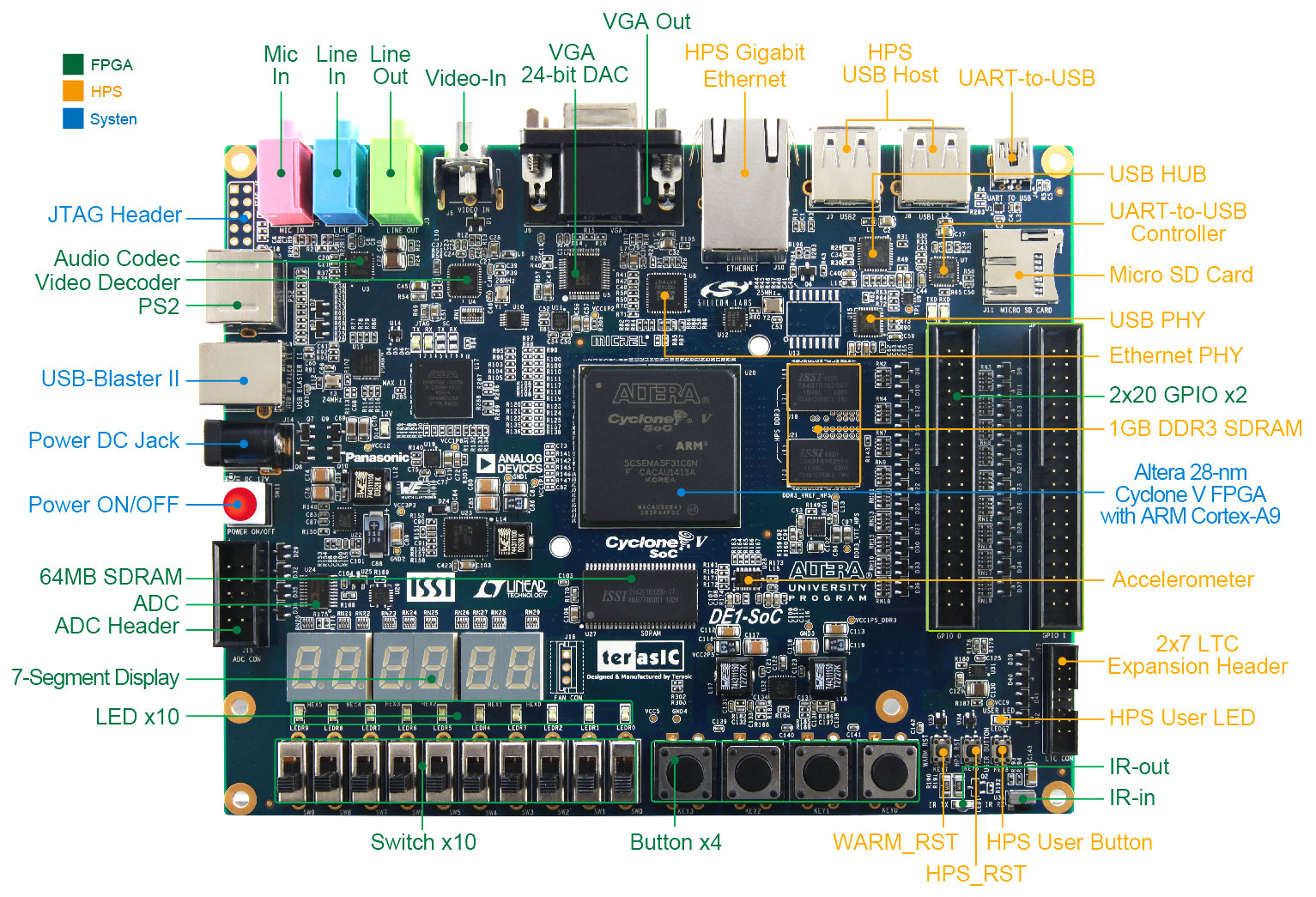

DE1-SoC by Terasic

The project based on the DE1-SoC development board from Terasic.

For more information check terasic DE1-SoC

Team

- Haberleitner David

- Posch Johannes

- Reisinger Thomas

- Steiger Martin

- Steinbacher Franz

- Wurm Michael

Project supervisor:

FH-Prof. Dipl-Ing. Dr. Markus Pfaff

Contact

University of Applied Science Upper Austria

Campus Hagenberg

Department Hardware-Software-Design

Project Audio Signal Processing SoC - ASP-SoC

mail: ASPSoC.fhHagenberg@gmail.com

© 2017